# Wire Transfer of Charge Packets Using a CCD-BBD Structure for Charge-Domain Signal Processing

Eric R. Fossum, Member, IEEE

Abstract—A structure for the virtual transfer of charge packets across metal wires is described theoretically and is experimentally verified. The structure is a hybrid of charge-coupled device (CCD) and bucket-brigade device (BBD) elements and permits the topological crossing of charge-domain signals in low power signal processing circuits. A test vehicle consisting of 8-, 32-, and 96-stage delay lines of various geometries implemented in a double-poly, double-metal foundry process was used to characterize the wire-transfer operation. Transfer efficiency ranging between 0.998 and 0.999 was obtained for surface n-channel devices with clock cycle times in the range from 40 ns to 0.3 ms. Transfer efficiency as high as 0.9999 was obtained for buried n-channel devices. Good agreement is found between experiment and simulation.

#### I. Introduction

CHARGE-coupled devices (CCD's) are presently the dominant technology for both image acquisition and readout. In the readout operation, charge is passed from under one electrode to the next by applying a sequence of clocking voltages. The charge transfer efficiency (CTE) is defined as the fraction of charge successfully transferred and in state-of-the-art CCD's, the CTE,  $\eta$ , can be as high as 0.99999 or more. In a large imager (e.g.,  $512 \times 512$ ), each packet must undergo several thousand transfers before reaching the output amplifier. In this case, the net transfer efficiency for a charge packet is  $\eta^m$ , where m is the total number of transfers. For example, if m = 3000 and  $\eta = 0.99999$ , the net transfer efficiency is of the other of 0.97. Such signal degradation is generally acceptable.

Recently there has been interest in placing analog image processing circuitry on the same chip as the imager [1]-[7]. Such circuitry might be used for noise reduction, spatial smoothing, nonuniformity correction, filtering, convolution, nonlinear local neighborhood operations, or image compression. The circuitry must be low-power and consume relatively little real estate. The use of the analog charge domain through CCD technology promises to fulfill these needs. However, since the CCD transfers charge between adjacent electrodes, the intimate, contiguous integration of circuitry makes the topological crossing of signal paths nearly impossible to achieve. Thus signal processing with CCD's has largely been confined to temporal filtering operations, with the CCD functioning primarily as an analog delay line.

A closely related technology to the CCD is the bucketbrigade device (BBD) [8]. While the BBD stores charge under MOS electrodes, it differs from the CCD in several respects. In

Manuscript received November 10, 1989; revised September 5, 1990. This work was supported by the NSF Presidential Young Investigator Award, Analog Devices, Inc., and Ford Aerospace. The review of this paper was arranged by Associate Editor W. F. Kosonocky.

The author was with the Department of Electrical Engineering, Columbia University, New York, NY 10027. He is now with Jet Propulsion Laboratory, M/S 300-315, Pasadena, CA 91109.

IEEE Log Number 9040641.

the BBD, electrodes overlap heavily doped regions of the semiconductor with the signal charge residing as majority carriers at the semiconductor surface. In the CCD, charge is stored as minority carriers at the surface of a moderately doped substrate (surface channel) or as majority carriers in a mostly depleted region buried below the surface (buried channel). A further distinction between the two technologies is that in the BBD charge is virtually transferred using a heavily doped junction between the electrodes (i.e., approximately the same number of carriers is recovered from the junction), while in the CCD charge is physically transported through an otherwise depleted region by the use of fringing fields between very closely spaced electrodes. The transfer efficiency of the BBD is generally much poorer than a CCD (typically 0.997) and also generally operates at lower frequencies (under 1 MHz).

In this paper, a hybrid structure combining features of the BBD and the CCD is described. Termed a wire-transfer structure, its main purpose is to permit topological crossing of charge-domain signals across metallic wires at high frequencies (0.1–100 MHz). Although the CTE of the wire-transfer structure is less than that of the CCD, the total number of transfers in the signal processing circuitry is much less than that occurring in image readout. Thus the total signal degradation occurring in the signal processing circuitry can be less than that occurring during image readout.

## II. WIRE-TRANSFER OPERATION

#### A. Concept

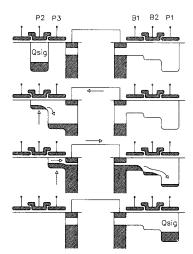

The wire-transfer structure is shown schematically in Fig. 1. For this discussion, a surface n-channel configuration is used, but p-channel or buried-channel configurations could be used as well. Two short CCD registers are shown connected by an output diode junction, a metal wire interconnect, and an input diode junction. It should be noted that unlike a BBD, no overlap between the heavily doped regions and the electrodes is desired. Initially, in the left (or output) register is a charge packet  $Q_{\text{sig}}$ that is to be transferred to the right (or input) register. Note that the initial voltage on the junctions corresponds to the channel under the first electrode of the input register (B1) being just pinched off. The charge is transferred in the usual CCD fashion from well P2 to P3 and charge sharing causes the voltage to rise on the junctions. The voltage on electrode P3 is then ramped down at a constant rate causing the ejection of the charge packet from under it. The channel under B1 and B2 is charged and a nearly constant current flows into the receiving well under electrode P1.

When the voltage on electrode P3 is fully ramped so that no charge remains under it, the junctions discharge into the input register with a time constant dictated by the total capacitance of the junctions and wiring. Ideally, the discharge ceases when

Fig. 1. Illustration of the wire-transfer process.

the channel under B1 returns to the pinchoff condition. Since the junction voltage is now equal to its initial value, it follows that the total charge injected into the input register is  $Q_{\rm sig}$ . It is noted that the charge transfer is virtual, that is, approximately the same number of charge carriers is injected into the receiving well as were output from under P3.

The maximum operating speed of the wire-transfer process can be designed to match that of the CCD. If the length and width of the barrier electrode (B1) have approximately the same dimensions as the electrodes in the CCD channel, electrode B1 need not be biased much above the MOS threshold voltage to accommodate the current source, provided the transition rate of the electrode P3 bias does not exceed the characteristic CCD transfer time. Electrode B2 is similarly designed. As in two-phase CCD's, low channel potentials under these electrodes increases bucket capacity of the structure. Buried-channel configurations may be expected to operate faster than surface-channel configurations reflecting the general speed difference between surface-channel and buried-channel CCD's [9]. Thus, wire-transfer in GaAs buried-channel (MESFET) CCD's might be expected to operate at over 1 GHz.

## B. Analysis

The analysis of the wire-transfer structure is similar to that of the BBD [8]-[13]. It is assumed that the structure is designed and operated such that the major effects which limit the CTE are subthreshold current conduction under electrode B1 and charge trapping in the vicinity of the junctions. While it will be shown that the former is readily relieved through the use of a bias charge (or "fat zero"), traps in the junction regions are a function of fabrication and not easily rectified.

The approach taken is to examine the subthreshold current flowing from the diode junctions and consequent change in junction voltage. Coupled with the node capacitance, the subthreshold current is shown to result in a trapping and emission process which degrades CTE. To begin the analysis, the current flowing under electrode B1 is modeled as [14]

$$I = I_s e^{-\beta V_n} \tag{1}$$

where  $V_n$  is the voltage of the junction relative to the junction pinchoff voltage,  $\beta$  is defined as q/kT, and  $I_s$  is the character-

istic current of the subthreshold conduction process scaling with the gate length of B1. Counter to intuition, analysis will reveal  $I_s$  to be a noncritical parameter. With the total capacitance of the junctions, interconnect wiring and other parasitics lumped as a constant  $C_n$ , it is readily shown that if the node (i.e., junction) is initially at voltage  $V_{n0}$ , then after time t, the node discharges and the voltage rises to voltage  $V_n(t)$  given by

$$V_n(t) = 1/\beta \ln \left[\beta I_s t/C_n + e^{\beta V_{n0}}\right].$$

(2)

In wire transfer, the node is initially biased by the current source  $I_{cs}$  generated by the ramping of electrode P3 such that

$$I_{cs} = C_b \, dV/dt \tag{3}$$

where  $C_b$  is the bucket capacitance under P3. Since the node voltage induced by this current source is generally small (approximately 100 mV), the subthreshold current expression of (1) can be approximately applied. Thus the node voltage under current source bias  $V_{ncs}$  is simply

$$V_{ncs} = 1/\beta \ln \left[ I_s / I_{cs} \right] \tag{4}$$

and is generally negative (relative to the pinchoff condition). In wire transfer, the discharge process continues for some characteristic clock cycle period  $T_c$  so that combining (4) and (2) yields

$$V_n(T_c) - V_{ncs} = 1/\beta \ln \left[\beta I_{cs} T_c/C_n + 1\right].$$

(5)

If m cycles pass without additional charge transferred into the node, the node voltage continues to rise to approximately

$$V_n(mT_c) - V_{ncs} = 1/\beta \ln \left[\beta I_{cs} mT_c/C_n + 1\right]$$

(6)

which is independent of the characteristic subthreshold current  $I_s$ . If the charge packet is now transferred into this discharged node, the charge retained by the node  $Q_{loss}$  after the packet is transferred out is determined simply by the node capacitance and the difference in voltage between (5) and (6). It is noted that the quantity  $I_{cs}T_c$  is of the order of the CCD bucket capacity. Thus the quantity  $\beta I_{cs}T_c/C_n$  is the ratio of the bucket capacity to a charge packet equal to  $C_n/\beta$ . Since this ratio is much greater than unity, one obtains the surprisingly simple result

$$Q_{\rm loss} \simeq C_n/\beta \ln [m] \tag{7}$$

which is proportional to the node capacitance and temperature. This result emphasizes the requirement for small node capacitances if losses are to be minimized.

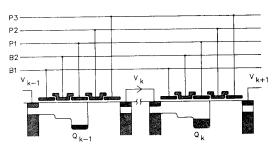

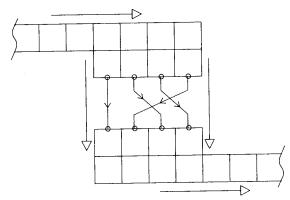

A shift register configuration using the wire-transfer structure is shown in Fig. 2. Although it is unlikely that such a shift register would be used in an actual signal processor, it is a useful vehicle for exploring the characteristics of the wire-transfer operation. Each shift register stage has five electrodes. Electrode B1 functions as the primary barrier gate for setting the quiescent node voltage and is typically dc biased. Electrode B2 serves to screen the potential under electrode B1 from any variation induced by charge residing under electrode P1 and is generally clocked. Electrodes B1 and B2 resemble the tetrode arrangement for the BBD [15]–[17]. Electrodes P1, P2, and P3 are the CCD-like portion of the wire-transfer structure. Operation of each stage proceeds like that illustrated in Fig. 1, with the addition of a CCD transfer cycle between electrode P1 and P2.

The transfer of charge from electrode  $P_{k-1}$  to electrode  $P1_k$  is now considered. Let the charge under electrode  $P1_{k-1}$  be  $Q_{k-1}$  and the voltage on the node between  $P1_{k-1}$  and  $P1_k$  be

Fig. 2. Schematic cross section of a shift register implemented using the wire-transfer structure. Gate B1 is typically dc-biased at a low level, while gate B2 is clocked approximately 1 V higher than the bias on B1. Gates P1-P3 are clocked as conventional 3-phase CCD's.

$V_k$ . The charge is first transferred to under P3 with CCD CTE of  $\eta_c$  so that the charge under electrode  $P3_{k-1}$  is  $\eta_c^2Q_{k-1}$ . The charge is then wire-transferred to under electrode  $P1_k$  in two steps. First, the bucket under  $P3_{k-1}$  is ramped to eject its charge in a current-source mode. At the end of this step, the node has been recharged to voltage  $V_k'$  such that

$$V_k' = V_k - \eta_c^2 Q_{k-1} / C_n \tag{8}$$

where  $C_n$  is the capacitance of the node (assumed constant). The recharged voltage  $V_k'$  saturates at  $V_{ncs}$  since the current source matches the receiving bucket injection current at this bias. The charge injected by the current source  $Q_{cs}$  into the receiving bucket under  $P1_k$ ,  $Q_{cs}$ , is approximately given by

$$Q_{cs} = \eta_w \left\{ \eta_c^2 Q_{k-1} - C_n [V_k - V_{ncs}] \right\}$$

(9)

where  $\eta_w$  is the wire-transfer efficiency. It should be noted that if  $V'_k$  fails to reach  $V_{ncs}$ , than  $Q_{cs}$  is taken to be zero.

In the second step, the node discharges and the voltage rises to  $V_k''$  determined by (2) above. The charge transferred to the receiving bucket in this step is

$$Q_{\text{disch}} = \eta_w \left\{ C_n [V_k'' - V_k'] \right\}$$

(10)

so that the total charge transferred  $Q_{tr} = Q_{cs} + Q_{disch}$  is simply

$$Q_{\rm tr} = \eta_w \Big\{ \eta_c^2 Q_{k-1} + C_n [V_k'' - V_k] \Big\}. \tag{11}$$

Noise in wire transfer is similar to that of BBD's [12]. The fundamental source of noise is in the discharge process. However, since the total charge transferred is the integral of the noisy discharge current, the rms noise charge  $Q_n$  varies as the square root of the total charge discharged. Thus

$$Q_n \simeq (qQ_{\rm disch})^{1/2}. (12)$$

The maximum value of  $Q_n$  is obtained for the maximum value of  $Q_{\rm disch}$ , which is  $Q_{\rm mip}$  as given below in (13) and appears as a kTC-type noise. While not reduced by a fat zero, the noise is a small fraction of the signal for large charge packets since most of the packet is transferred during the first step of the process as  $Q_{cs}$ .

#### C. Simulators

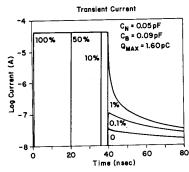

In order to check the accuracy of these charge-domain expressions, a computer program was written to simulate the wire-transfer process in the time (current) domain. Excellent agreement was obtained between the simulation and the charge-domain expression above. The injection current is shown as a function of time in Fig. 3. Note that with the exception of very

Fig. 3. Calculated current transient under the B1 electrode for various charge packet sizes.

small charge packets, the final current or node voltage is independent of charge packet size. This helps insure high CTE.

A second computer simulation program was written to simulate the transfer of charge in an m-stage shift register using the charge-domain expressions derived above. The program included the nonlinear capacitance of the node. A charge packet was injected into the shift register which was preceded by m empty packets. The resultant output is significantly different in character than that found using a simple proportional-loss model (the usual CTE model). In the latter, an exponentially decaying tail is predicted. In the case of wire transfer, the tail decays much more slowly. Furthermore, the first trailing packet reaches a limiting value and saturates (if  $\eta_w$  is unity). This can be shown analytically by considering (11) in the case where  $V_k$  is set by a prior, relatively large charge packet. In this case,  $V_k$  is given by (5) and one seeks the value of  $Q_{k-1}$  such that  $V_k'' = V_k$ . This insures that  $Q_{tr} = Q_{k-1}$  and a steady state is reached. After some algebra, one obtains the maximum trailing packet  $Q_{mip}$  as

$$Q_{mtp} = C_n/\beta \ln \left[\beta I_{cs} T_c/C_n\right] \tag{13}$$

which scales approximately linearly with node capacitance but which is relatively insensitive to  $T_c$ . One can also reach the same result intuitively by arguing that in steady state, the injected charge packet just fills the node to  $V_k' = V_{ncs}$ , and the node discharges to  $V_k'' = V_k$ . The charge packet required for steady state is simply the voltage expressed by (5) multiplied by the node capacitance. Thus an alternative interpretation of  $Q_{mip}$  is that it is the minimum charge packet required for a "fat zero." In general,  $Q_{mip}$  is quite small and the use of such a "thin zero" prevents transfer inefficiency due to subthreshold effects.

### III. EXPERIMENTAL

# A. Layout and Fabrication

To experimentally verify the wire-transfer concept and theory, a test vehicle was designed and sent to a commercial CCD foundry for fabrication. The test vehicle consists of eight wire-transfer shift registers of various configurations, and a conventional 96-stage, 4-phase CCD shift register. A double-poly, double-metal, n-channel surface technology was used with a transfer electrode length of 3.5  $\mu m$  corresponding to a theoretical CCD transfer time of 20 ns for a CTE of 0.999 [18]. The channel width was 50  $\mu m$ , yielding a bucket capacity of 425 000 carriers /V. The devices were fabricated on a p/p+ substrate with the p-layer nominally 10  $\Omega$  · cm. All shift registers have a fill-and-spill input stage at the front end and terminate with a

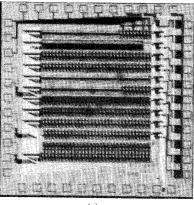

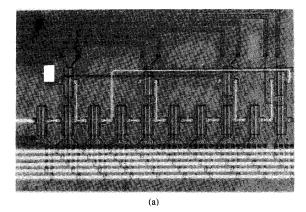

two-stage source-follower output amplifier with dual-gate reset, on-chip load and on-chip sample-and-hold. The amplifier was designed to drive a 1-M $\Omega$ -22-pF oscilloscope directly. The nominal shift register had 32 stages (each as shown in Fig. 2) with a B1 gate length of 3.0  $\mu$ m and a B2 gate length of 2.5  $\mu$ m in accordance with the nominal minimum design rules of the foundry. The input and output junctions were 2  $\mu m$   $\times$  50  $\mu m$ with additional area for contacts. An 8-stage and a 96-stage shift register with the same geometry were included. The 96-stage register is snaked resulting in a few interconnect wiring lengths of several hundred micrometers. Two 32-stage shift registers with altered geometry to explore design sensitivity were also included. One has B1/B2 lengths of 2.5/2.5  $\mu$ m (smaller barrier) and the other has B1/B2 of  $3.5/3.0 \mu m$ . Each of these five shift registers uses the second level of metal for interconnect between stages. The total node capacitance for each interconnect (including junction capacitance) was estimated to be 0.05 pF. Two other shift registers were included to test the effect of node capacitance. One has additional second-level metal wiring capacitance (0.02 pF) to simulate an interconnect length of 150 µm and the second has an intentional bootstrap capacitance (0.01 pF) between the node and B1 in an attempt to reduce the effect of transient substrate currents on node bias. A photograph of the test vehicle is shown in Fig. 4(a), and a closeup of the nominal shift register stage in Fig. 4(b).

#### B. Test Procedure

Several wafers from several lots were tested at the wafer level using a wafer prober. Two wafers were selected for dicing and packaging. The packaged devices were tested in a shielded test box using clock voltages derived from a Pulse Instruments PI-5800 timing generator and PI-453 MOS CCD clock drivers. These drivers have a maximum slew rate of approximately  $0.2\,V/ns.$

The shift registers were operated as three-phase devices with overlapping waveforms. Each phase had a 50% duty cycle with a total period of six clock cycles on the PI-5800. Thus the wire-transfer portion occupied two clock cycles, or one clock cycle for each of the two steps. In this paper, the single-clock-cycle time ( $T_c$ ) is reported as the operating speed of the device, whereas the total time to transfer from one stage to the next (one wire transfer and two CCD transfers) takes six clock cycles.

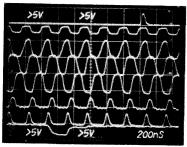

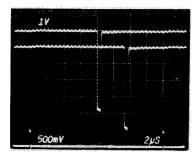

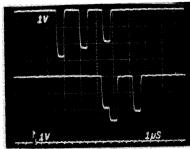

Electrode B1 was typically dc biased at 1.0 V using a precision power supply, electrode B2 clocked with an adjustable peak voltage typically 1.0 V, higher than B1, and electrodes P1, P2, and P3 clocked with a common peak voltage typically 16 V. The substrate was grounded and the low level for all clocked signals was ground. A photograph of the applied clock waveforms is shown in Fig. 5.

Charge transfer efficiency was characterized for worst case operation in which a single full charge packet is loaded into a shift register with 100 empty following charge packets to examine the subthreshold node leakage. The output charge packet is distorted by loss due to subthreshold effects, wire-transfer efficiency, and CCD transfer efficiency. The measured CTE is approximately given in this case by

$$\eta = \left\{ Q_1 / (Q_1 + Q_2 + Q_3 \cdots) \right\}^{(1/m)} \tag{14}$$

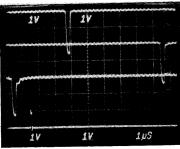

where  $Q_1$  is the first charge packet,  $Q_2$  is the first trailing charge packet,  $Q_3$  the second trailing charge packet, etc. Fig. 6 is an

(a)

(b)

Fig. 4. (a) Microphotograph of the wire-transfer test vehicle chip. (b) Closeup of shift-register stage.

Fig. 5. Oscilloscope photograph showing applied clocking waveforms. Traces, from top to bottom, are voltage pulse for generating charge packet,  $V_{B2}$ ,  $V_{P1}$ ,  $V_{P2}$ ,  $V_{P3}$ , amplifier reset, sample-and-hold, and output of 96-stage register ("wrapped" around screen).

oscilloscope photograph showing the output of the 8-stage, 32-stage, and 96-stage shift registers for a clock cycle time of 40 ns. The invariance of total output charge between the three different length registers indicates that fixed loss does not dominate device behavior. However, deferred charge clearly depends on register length.

Fig. 6. Oscilloscope photograph showing the delayed output of the shift registers following input of single packet. Top trace, second trace, and third trace show output of 8-, 32-, and 96-stage shift registers, respectively. Lower trace shows voltage pulse for generating charge packet. Note that third trace is "wrapped" around screen. 100 empty packets (no fat zero) follow input packet. Clock cycle time was 40 ns.

#### C. Results

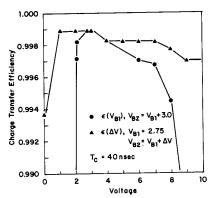

The CTE was measured for each shift register for several clock cycle times. The CTE was found to be nearly independent of cycle time for the cycle times tested, which ranged from 40 ns to 0.3 ms, provided the voltage on B1 was adjusted to be higher for the shorter cycle times (to insure sufficient conductance under B1 to accommodate the higher value of  $I_{cs}$ ). Over these times, the CTE for the nominal geometry shift registers was approximately 0.9985 with an experimental accuracy of 0.0005. For the altered geometry shift registers, the smaller barrier length had lower CTE than the nominal register, and the longer barrier length had higher CTE. However, the spread was only approximately 0.0005, close to the limits of experimental accuracy and was not consistent leading to inconclusive results with respect to optimal barrier gate sizing. For the registers with additional node capacitance, the CTE was degraded as expected. The shift register with additional wiring capacitance exhibited CTE of approximately 0.9970 and the shift register with the bootstrap capacitance had a CTE of approximately 0.9960. Furthermore, the bootstrap arrangement was more susceptible to low-frequency coupling to the substrate leading to the conclusion that the bootstrap approach is inferior in the case of heavily doped substrates. The CTE for the 96-stage 4-phase CCD was tested and found to exhibit CTE exceeding 0.9999, indicating that the CCD portion of the transfer process does not limit overall device behavior.

Closer examination of the deferred charge observed in Fig. 6 reveals that it appears to have two components. The first is represented by the first trailing packet, which scales with signal size. This proportional behavior, which dominates the measured CTE, is termed  $\eta_w$ , the wire transfer efficiency, and includes all trapping effects at the junction diode surface discussed later. The second component of the deferred charge is a much smaller series of trailing charge packets commencing with the second trailing packet and which slowly decay in amplitude. The amplitude of this series, 1% to 2%, of the full-well packet size, is nearly independent of the size of the primary and first trailing packets. This deferred charge is attributed to the subthreshold effect.

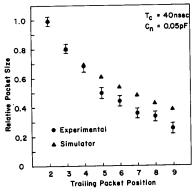

Using  $\eta_w$  as an adjustable parameter in the shift register simulator, and including the subthreshold effect, reasonable fitting of the observed trailing packets in the nominal geometry shift registers was obtained using  $\eta_w$  approximately equal to 0.9988 as shown in Fig. 7. Without including the subthreshold effect, a proportional loss model cannot be sensibly fitted to the ex-

Fig. 7. Relative size of trailing charge packets (normalized to second trailing packet) as a function of packet output position measured experimentally and simulated

Fig. 8. Charge transfer efficiency as a function of B1 and B2 bias voltages.

perimental data. Note that the trailing packets are normalized to the second trailing packet. With subthreshold effect charge loss, the net CTE agrees with the experimental CTE of 0.9985.

The nominal geometry 96-stage wire-transfer shift register was also tested for other combinations of duty cycle, where duty cycle is defined as the ratio of number of full charge packets to number of empty packets. For duty cycles ranging from 0.01 to 100, the CTE of the register appeared to remain constant, confirming that fixed-loss effects do not dominate device behavior. Fixed losses, expected from (7), may be ameliorated by dark current in the junction diodes which refill charge lost to subthreshold leakage providing the thin zero described above.

For a fixed cycle time, the effect of electrode B1 and B2 bias voltages was investigated. The measured CTE as a function of these voltages is shown in Fig. 8. The dc voltage on electrode B1 is not overly critical provided it is greater than the MOS threshold voltage. The voltage range for B2 was more robust provided it was biased greater than B1.

A wafer with a buried-channel implant was also tested. The major difference between the buried-channel and surface-channel devices (from the perspective of the wire-transfer model) is that the node is n<sup>+</sup>/n and there is no depletion region edge in the heavily doped region. Thus the effect of carrier trapping in the vicinity of the junction should be reduced. The node capacitance is also lower implying lower loss due to subthreshold effects. Indeed, the buried-channel devices were found to have CTE as high as 0.9999 which is attributed to these factors (rather

than increased speed) since the CTE in the surface-channel devices was not a function of operating frequency.

The CTE of the surface-channel devices varied from lot to lot and poor CTE correlated with poor junction diodes. The conclusion is drawn that charge trapping in the vicinity of the junction diodes is presently limiting the performance of the wire-transfer process. However, CTE did not appear to vary significantly from wafer to wafer or device to device in the final lot tested, and is attributed to deliberate fabrication of higher quality junctions.

The ability of the screen electrode (B2) to prevent barrier height modulation under electrode B1 was tested using a single shift register stage with an external connection to both junctions. Using a pulsed charge domain measurement, similar to that employed by Scott and Chamberlain [13], a relative measurement of the potential  $\psi_{B1}$  under B1 could be made. The transfer function  $d\psi_{B1}/dV_{B2}$  was measured for each of three gate geometries. It was found that the transfer function was approximately 20, 30, and 50 mV/V for the 3.5/3.0, 3.0/2.5, and 2.5/2.5 B1/B2 geometries, respectively. The screened transfer function for P1 ( $d\psi_{B1}/dV_{P1}$ ) was then measured and found to be approximately 0.7 mV/V, indicating excellent screening by the 2.5- $\mu$ m B2 electrode.

The noise floor in the measurements was dominated by residual 60-Hz and RF noise in the test station, with a value on the order of 2 mV. Thus the measured dynamic range (defined as 20 log SNR) was 62 dB independent of shift register length. However, using the expression in (12) with a full bucket equal to  $4 \times 10^6$  carriers and  $Q_{mip}$  equal to  $4.4 \times 10^4$  carriers, one obtains a noise level of 210 carriers per transfer, or a theoretical dynamic range of 65 dB after 96 transfers.

#### IV. ROUTING AND PARALLEL LOAD

## A. Router

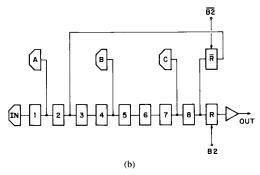

As discussed in the Introduction, the primary function envisioned for wire transfer is the topological crossing of signals in charge-domain signal processing circuits. However, wire transfer allows other functions such as summation and routing to be performed as well. An experimental test site was included on the wire-transfer test vehicle chip for exploring this concept. As shown in Fig. 9, the test site consists of eight shift register stages. The ninth stage is a router structure consisting of two parallel stages with the input diode junctions connected together. The stages' electrodes are tied in parallel with the exception of the B2 electrodes. These electrodes are used for steering the charge packet (current source) to one stage or the other in manner similar to that proposed by Heller [19].

To test the router, a single charge packet is loaded into the shift register input and shifted to the router. The router is clocked to cause the charge packet to be steered into the upper register. The output of the upper register is tied back to the node following the second stage register. Thus the routed charge packet is summed with the output of the second stage and loaded into the third stage. However, in the experiment, only empty packets followed the initial packet. The charge packet is again clocked toward the end of the shift register. In one timing pattern, the charge packet is allowed to pass on to the output amplifier. In a second timing pattern, the charge packet was diverted a second time and looped back to the output of the second stage before being allowed to pass to the output amplifier. A double-exposure oscilloscope photograph illustrating this programmed delay function is shown in Fig. 10.

Fig. 9. (a) Photograph of router/parallel-load experiment. (b) Block diagram of router/parallel-load experiment.

Fig. 10. Double-exposure photograph showing output of shift register for one programmed loop (top trace) and two loops (second trace). Lower trace shows voltage pulse for generating charge packet.

The ability of the router to effectively steer charge packets can be measured by examining the residual charge leaking through the nonselected stage. The ratio of the magnitude of the routed packet to the leakage is a measure of the router rejection ratio. This ratio was found to be approximately 600:1.

If both B2 electrodes in the router stage are selected, the input charge packet is split between the two receiving wells. One charge packet is transferred to the output amplifier while the other is recirculated and split a second time. This process is repeated yielding output packets split in powers of two. This splitter mode worked unexpectedly well with split accuracy of better than 1%. Splitting and programmable routing make the implementation of a charge-domain multiplying digital-to-analog converter (MDAC) straightforward [7].

Fig. 11. Double-exposure photograph showing output of shift register following parallel load of 3 charge packets (top trace) and following load and recirculation of first packet (second trace). Lower trace shows voltage pulse for generating charge packet.

Fig. 12. Block diagram of serial/parallel-parallel/serial circuit for arbitrary reordering of serial charge packet data stream using wire transfer.

#### B. Parallel Load

In addition to the router loop-back on this test site, a parallelload structure was also included. Three charge packets,  $Q_a$ ,  $Q_b$ , and  $Q_c$  can be simultaneously generated and summed using wire transfer with the outputs of stages 1, 4, and 7, respectively, thus effecting a parallel-to-serial multiplexing operation. The top trace of Fig. 11 demonstrates this function. The charge packet router was programmed to recirculate packets  $Q_c$  and  $Q_b$  thereby changing the sequential order of output packets from  $Q_c$ - $Q_b$ - $Q_a$ to  $Q_a - Q_c - Q_b$ , as illustrated in the lower trace of Fig. 11.

Changing the serial order of charge packets in a data stream is an important function for focal-plane image processing, particularly in the case of pyramid compression schemes [20]. The use of a router is a programmable means for performing this function. However, a simple CCD serial-parallel conversion, followed by wire-transfer reordering and finally CCD parallelserial conversion can be used more effectively for hard-wired applications, as illustrated in Fig. 12.

# V. SUMMARY

A structure for the virtual transfer of charge packets across metal wires has been analyzed theoretically and simulated by computer. An experimental test vehicle was fabricated and demonstrated good performance over a wide frequency range. The observed CTE of the structure ranged between 0.998 and 0.999 for surface-channel devices, and was as high as 0.9999 for buried-channel devices. The devices were found to be robust with respect to bias voltages and clock waveforms.

In the experimental devices described in this paper, the test

station was the limiting consideration for both speed and dynamic range performance. The minimum clock cycle time used was 40 ns and the maximum dynamic range was approximately 62 dB, limited by residual 60-Hz and RF noise in the test sta-

The wire-transfer process allows for the topological crossing of signal charges in charge domain signal processing circuitry. The wire-transfer structure also facilitates corner turning, changing channel width, and the programmable steering of charge packets. The wire-transfer structure also makes charge summation and charge packet splitting readily achievable. The structure provides a degree of design flexibility and methodology previously denied CCD circuit designers.

#### ACKNOWLEDGMENT

The author wishes to thank S. Kemeny for help in the SPICE simulation of the output amplifier as well as for useful discussions. The author also appreciates an illuminating discussion on the fundamental aspects of noise in wire transfer with Prof. M. Teich. The assistance of Dr. R. Bredthauer of Ford Aerospace in the fabrication of these devices was invaluable. This manuscript was written at JPL/Caltech during a visit hosted by Dr. C. Stevens.

#### REFERENCES

- [1] E. R. Fossum, "Charge-coupled computing for focal-plane image preprocessing," Opt. Eng., vol. 26, no. 9, pp. 916-922,

- [2] J. Joseph, P. C. T. Roberts, J. A. Hoschette, B. R. Hanzal, and J. C. Schwanebeck, "A CCD-based parallel analog processor," Proc. SPIE, vol. 501, pp. 238-241, 1984.

- [3] E. S. Eid and E. R. Fossum, "IRET—A CCD focal plane image processor chip," *Proc. SPIE*, vol. 1107, pp. 196-200, 1989.

[4] P. R. Beaudet, "CCD focal convolver (smart eyeball)," pre-

- sented at the Optical Society of America Topical Mtg. on Machine Vision, paper FD6/1-4, Incline Village, NV, Mar. 1985.

J. C. Carson, "Applications of advanced 'Z' technology focal-

- plane architectures," *Proc. SPIE*, vol. 930, p. 18, 1987. E. R. Fossum, "Architectures for focal-plane image processing," *Opt. Eng.*, vol. 28, no. 8, pp. 865–871, 1989.

- [7] S. E. Kemeny, E. S. Eid, and E. R. Fossum, "Novel CCD image processor for Z-plane architecture," *Proc. SPIE*, vol. 1097, pp. 66–72, 1989.

- [8] F. Sangster, "Integrated MOS and bipolar analog delay lines

- using bucket brigade storage," in *Int. Solid State Circuits Conf.*, *Dig. Tech. Papers*, pp. 74–75, 1970.

M. Barron, B. Kurz, and W. Butler, "Application of JFET-MES-FET devices to bucket brigade circuits," in *Proc. 17th IEEE Int.* Electron Devices Meet., p. 76 (Washington DC, 1971).

[10] K. K. Thornber, "Incomplete charge transfer in IGFET bucket

- brigade shift registers," IEEE Trans. Electron Devices, vol. ED-

- 18, no. 10, pp. 941-950, 1971.

C. Berglund and H. Boll, "Performance limitations of the IGFET bucket-brigade shift register," *IEEE Trans. Electron Devices*, vol. ED-19, no. 7, pp. 852-860, 1972.

- [12] D. Buss, W. Bailey, and W. Eversole, "Noise in MOS bucket brigade devices," *IEEE Trans. Electron Devices*, vol. ED-22, no. 11, pp. 977-981, 1975.

- [13] D. Scott and S. Chamberlain, "Modeling and experimental simulation of the low-frequency transfer inefficiency in bucket brigade devices," IEEE Trans. Electron Devices, vol. ED-27, no. 2, pp. 405-414, 1980

- [14] E. S. Yang, Microelectronic Devices. New York, NY: Mc-Graw-Hill, 1988.

- F. L. J. Sangster, "Integrated bucket-brigade delay line using MOS tetrodes," *Philips Tech. Rev.*, vol. 31, p. 266, 1970.

M. Itoh, M. Shikata, T. Gobara, T. Kimura, H. Oishi, and S.

- Arita, "A novel BBD structure for low voltage operation," Proc. 1982 IEEE Int. Electron Device Meet., pp. 119-122, 1982.

R. M. Barsan and A. Delibaltov, "Non-overlapping dual-gate

- bucket-brigade devices," Appl. Phys. Lett., vol. 36, no. 4, pp. 329-331, 1980.

- [18] L. G. Heller, W. H. Chang, and A. W. Lo, "A model of charge transfer in bucket brigade and charge-coupled devices," *IBM J. Res. Develop.*, vol. 16, pp. 184-187, 1972.

[19] L. G. Heller, "Bucket brigade charge packet diverter," *IBM*

- [19] L. G. Heller, "Bucket brigade charge packet diverter," *IBM Tech. Disclosure Bull.*, vol. 18, no. 8, pp. 2733-2734, 1976.

[20] S. E. Kemeny, H. Meadows, and E. R. Fossum, "CCD-based

- [20] S. E. Kemeny, H. Meadows, and E. R. Fossum, "CCD-based scheme for on-chip reorganization of image data for lossless image compression," CTR Tech. Rep. 160, Columbia University, New York, NY, 1989.

Eric R. Fossum (S'80-M'84) received the B.S. degree in physics and engineering from Trinity College, Hartford, CT, in 1979, the M.S. degree in 1980 in applied physics, from Yale University, New Haven, CT, and the Ph.D. degree from Yale in electrical engineering in 1984.

During the summers of 1981, 1982, and 1983 he was with the Hughes Aircraft Company in Canoga Park, CA, working on various problems related to infrared focal-plane array detector and readout structures. He has held an IBM Graduate Fellowship and the Howard Hughes Doctoral Fellowship. In 1984, he joined Columbia University, New York, NY, as an Assistant Professor and was engaged in research on charged-coupled devices in both silicon for focal-plane image processing and GaAs for very-high-speed signal processing. Other activities included novel devices and structures for fiber-based optical interconnects and the low-energy ion beam modification of semiconductor surfaces. He was promoted to Associate Professor in 1989. In 1990, he joined the Jet Propulsion Laboratory, Pasadena, CA, as Assistant Section Manager for Imager Research and Advanced Development and continues his own research in focal-plane image processing and III-V CCD's. He received the IBM Faculty Development Award in 1984 and was named an NSF Presidential Young Investigator in 1986. Also in 1986, he organized and chaired the IEEE Workshop on Charge-Coupled Devices. In 1989, he was appointed as a distinguished Visiting Scientist at the Jet Propulsion Laboratory. In 1990, he organized and co-chaired the IEEE Workshop on Advanced Solid-State Imagers. He has published over fifty technical papers and holds several patents.

Dr. Fossum is a member of SPIE, APS, and AVS.