# PROCEEDINGS OF SPIE

SPIEDigitalLibrary.org/conference-proceedings-of-spie

Quanta image sensors: Photonnumber-resolving megapixel image sensors at room temperature without avalanche gain

W. Deng, S. Masoodian, J. Ma, E. R. Fossum

W. Deng, S. Masoodian, J. Ma, E. R. Fossum, "Quanta image sensors: Photon-number-resolving megapixel image sensors at room temperature without avalanche gain," Proc. SPIE 10659, Advanced Photon Counting Techniques XII, 1065902 (14 May 2018); doi: 10.1117/12.2309631

Event: SPIE Commercial + Scientific Sensing and Imaging, 2018, Orlando, Florida, United States

# Quanta Image Sensors: Photon-Number-Resolving Megapixel Image Sensors at Room Temperature without Avalanche Gain

W. Deng<sup>1</sup>, D. Starkey<sup>1</sup>, S. Masoodian<sup>2</sup>, J. Ma<sup>2</sup> and E.R. Fossum<sup>1</sup>

<sup>1</sup>Thayer School of Engineering, Dartmouth College, Hanover, NH USA 03755;

<sup>2</sup>Gigajot Technology, Inc. Pasadena, CA USA 91107

# **ABSTRACT**

This paper reports on the state of the art of the Quanta Image Sensor (QIS) being developed by Dartmouth. The QIS is a photon-counting image sensor. Experimental 1Mpixel devices have been implemented in a modified backside-illuminated stacked CMOS image sensor process. Without the use of avalanche multiplicative gain, the sensors have achieved room temperature average read noise of 0.22e- rms (analog readout) permitting photon counting, and over 1000fps readout at under 20mW total power dissipation including pads (single-bit digital readout).\*

Keywords: Photon counting detector, quanta image sensor, QIS, CMOS image sensor, CIS, charge-transfer amplifier

# 1. INTRODUCTION

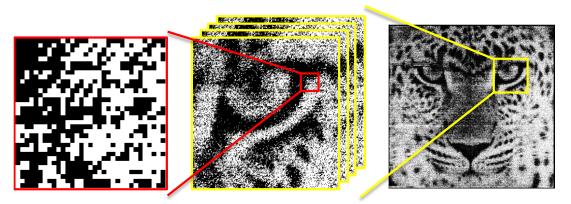

The Quanta Image Sensor (QIS) was introduced in 2005 as a possible paradigm shift in image capture to take advantage of shrinking pixel sizes enabled by technological advancements [1]. Conceptually, the QIS contains a large number of sub-diffraction-limit, high-conversion-gain, low-full-well-capacity pixels, called "jots." The key aspects of the QIS involve counting individual photoelectrons using the jots at high readout rates, representing this binary output as a bit cube (x,y,t), and finally, processing the bit cubes to form high dynamic range images [2]. The QIS concept is illustrated in Figure 1.

Figure 1. QIS concept. Bit-plane images are captured at high frame rate, where a logic 0 corresponds to no received photoelectron, and a logic 1 corresponds to at least one received photoelectron. The bit-planes are then logically stacked in time, and grey-scale pixels are formed from a "cubicle" of bits in a spatial and temporal neighborhood. The extent of the neighborhood can be set on the focal-plane, or by software coding after capture.

Advanced Photon Counting Techniques XII, edited by Mark A. Itzler, Joe Campbell, Proc. of SPIE Vol. 10659, 1065902 · © 2018 SPIE · CCC code: 0277-786X/18/\$18 · doi: 10.1117/12.2309631

<sup>\*</sup> Much of this invited paper, 1065902, is replicated for a simultaneous meeting as invited paper 106391Q.

Conceptually, a QIS may contain over a billion jots if the pixels are small enough (e.g. <500nm pitch) with readout speed primarily limited by allowable power dissipation in getting the data off the sensor. For example, a billion jots at 1000fps corresponds to 1Tb/s data rate for single-bit digital output.

While initially conceived as a possible next-generation consumer image capture device, once it was demonstrated that we could reliably detect single photoelectrons with low bit-error rate (BER), it became apparent that the device has more immediate application to scientific imaging than consumer imaging.

Progress on the device was reviewed in 2016 [2] and technical results most recently reported at the end of 2017 [3]. This paper summarizes some of these results as they pertain to scientific imaging, including some recent measurements at cooled temperatures as we try to understand current noise limitations. We also preliminarily report, for the first time, on QIS devices implemented with JFETs, although the JFET work remains underway and thus far has not yielded the same high performance as MOSFET readout.

# 2. SENSOR

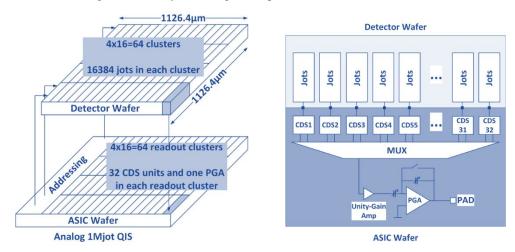

# 2.1 Cluster-parallel sensor readout architecture

The simplified cluster-parallel readout architecture of the imager is shown in Figure 2. The stacked BSI QIS uses two substrates, with the substrates being stacked vertically and electrically connected by a dense 2D array of hybrid bonding pads, with the photo-detectors and circuits on different substrates. The jots are implemented on the detector substrate using a simplified 45nm technology-node process, and the readout circuits and addressing circuits are located on the ASIC substrate using a 65nm technology node and using larger-than-minimum gate lengths to handle the large input common mode range that results from the different jot designs. Each cluster of jots is associated with its own dedicated readout electronics stacked under the cluster. Twenty (20) different 1Mjot arrays are implemented in this chip, where the arrays have different variations of jot and readout design. There were two classes of readout designs, one supporting analog readout for detailed characterization, and one supporting binary data readout at much higher field rates. In this paper we will focus on the slower analog readout arrays. The digital output was described in more detail in [4].

Figure 2. Simplified architecture of 1Mjot stacked QIS (analog readout).

The jots are two-way shared 2(H)x1(V) and clusters are 256 rows x 64 columns in size (16,384 jots/cluster) resulting in 4x16 array of clusters (64 clusters) for readout. The 64 columns of a cluster are multiplexed to 32 CDS processors, and the 32 CDS outputs are multiplexed to a single programmable gain amplifier, with gain set at 10x for most results described in this paper. There are 64 of the CDS/mux/PGA units on the readout layer that are connected to 16 analog pads which go to an off-chip 14-bit ADC for quantization.

# 2.2 Jot devices

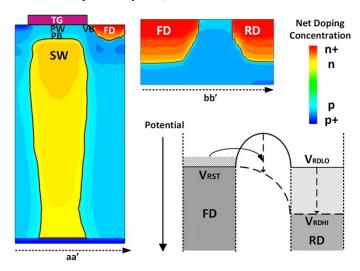

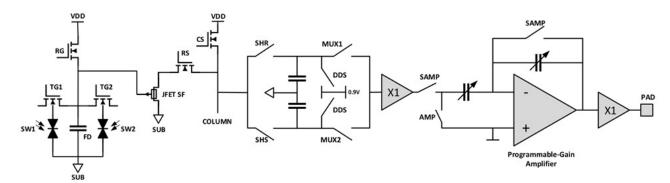

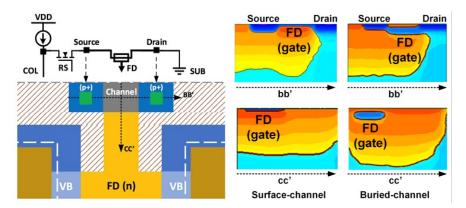

The analog-output array characterization is reported in this paper. Several types of jots were implemented in the arrays, some with different geometries. The photodiode, storage well (SW), transfer gate (TG) and floating diffusion (FD) portions of the jot, common to all devices, are shown in Figure 3. The jot layer is fabricated with a slightly modified 45nm BSI CMOS image sensor (CIS) process. In essence, a buried photodiode has been created below a transfer gate called the pump gate. The pump-gate photodiode and storage well doping profile is adapted from our previously demonstrated design and optimized for an improved effective fill-factor and better response in the shorter wavelength regime. The fabrication of the jots followed the baseline CIS process flow, while implantation modifications were made to realize the desired doping profiles for the various structures. The schematic of the 2-way-shared jots is shown in Figure 4. These jots include MOSFET source-follower (SF) output devices and JFET SF output devices. The MOSFET SFs were implemented as both buried-channel (BC) and surface-channel (SC) devices, and the reset for the output floating diffusion (FD) of these devices was either a tapered-reset-gate MOSFET (TPG) or a punch-through-reset (PTR) device (shown in Figure 3). The MOSFET devices and reset devices were described previously [3,4].

Figure 3. (Left) Cross-section of doping profile from 3D TCAD simulation of pump-gate jot. (Right) Punch-through reset (PTR) device doping profile and potential well schematic of reset of floating diffusion (FD).

The JFET SFs, modeled in [5], also have TPG or PTR reset, but only the TPG JFET SF jots have been characterized so far. The JFETS were implemented as a surface-channel device (gate under the channel) or as a buried-channel device, meaning that the JFET gate was wrapped around the channel, above and below, and a new special JFET symbol has been used in the schematics. For reasons likely related to implant conditions, the surface-channel devices are poorly behaved and so only the TPG buried-channel JFET jots are reported here. Cross-sections of the two JFET configurations are shown in Figure 5.

Figure 4. Schematic of readout signal chain for analog output (JFET source-follower shown).

Figure 5. (left) Simplified layout and simulated doping profile of the JFET jot pair; (right) cross section cuts of buried-channel and surface channel JFET showing wrap-around gate which is integrated with the floating diffusion gate.

# 2.3 Sensor function

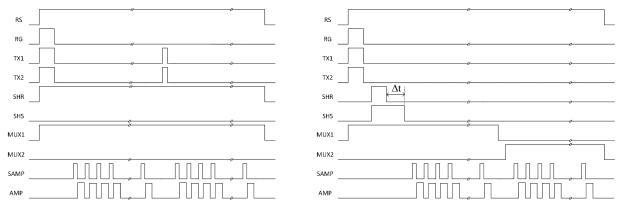

The sensor is readout using a rolling shutter like conventional CMOS image sensors. After a row is selected, the jots are reset. The reset level is readout through the signal chain of Figure 4. However, in the reported measurements, only one branch of the CDS unit was used with the SHR and MUX1 switches always closed for photon counting histogram (PCH) testing. Figure 6 (left) shows a timing diagram illustrating the testing methodology. The PGA is set to a gain of 10x. The reset level is amplified and sampled by the off-chip ADC 42 times at 667 kHz. After the TX gates have been pulsed, the new signal level is amplified and sampled by the ADC another 42 times. The reset level is determined by taking the mean of 38 of the 42 samples taken by the ADC for the reset level and the signal level is calculated similarly. CDS is performed digitally by subtracting these two values.

Figure 6. Timing diagram used for PCH testing (left) and SF noise testing (right).

# 3. EXPERIMENTAL RESULTS

#### 3.1 Room temperature characterization

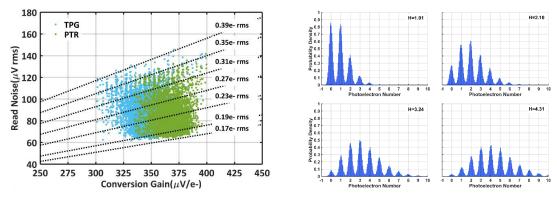

The TPG jots and PTR jots were first tested at room temperature (RT). Figure 7 (left) shows a scatter plot of the voltage-referred read noise versus the conversion gain from an array of 256(H)x32(V) jots. The electron-referred noise levels are also illustrated as references using dashed lines. The conversion gain (CG) and read noise were determined using the PCH method [6]. The PCH of each jot was created by continuously reading the jot output for 20k times. Based on the PCH, the read noise can be extracted using valley-to-peak modulation (VPM). The conversion gain, which equals to the voltage signal generated per photoelectron, can be determined from the peak-to-peak distance.

The TPG jots showed 0.23e- rms read noise on average, while the PTR jots showed 0.21e- rms read noise on average. The PTR jots have a lower noise due to the lower FD parasitic capacitance thus the higher CG:  $345\mu\text{V/e}$ - for the TPG jots and  $368\mu\text{V/e}$ - for the PTR jots on average. The variability in the fabrication process, such as mask misalignment, leads to the

CG variation. The trap number randomness may cause the source follower (SF) voltage noise variation. A PCH from a PTR jot with 0.17e- rms read noise under 4 different illumination levels is shown in Figure 7 (right). The quantization of photoelectron number can be clearly observed, demonstrating the room temperature photoelectron counting capability.

Figure 7. (left) A scatter plot of the voltage-referred read noise versus conversion gain of TPG jots and PTR jots; (right) Experimental demonstration of photoelectron counting from a PTR jot with different quanta exposure H.

#### 3.2 Low temperature characterization

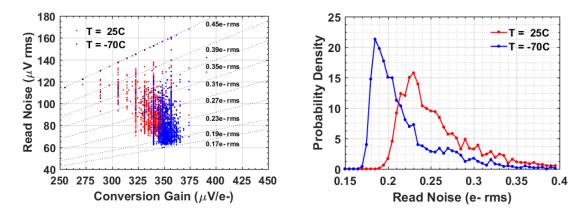

The read noise is dominated by the in-pixel SF 1/f noise. In order to understand the noise limitations, low-temperature testing was carried out. The nature of the noise may be discerned from the noise trend with temperature. In this measurement, an array of 256(H)x8(V) TPG jots was tested. The SF was biased at 1  $\mu$ A. A PCH was generated for each jot from continuous 20k read values under a stable illumination. The extraction of CG and read noise is based on the PCH method.

As shown in Figure 8 (left), a scatter plot of the voltage-referred read noise versus CG of TPG jots at 25C and -70C is presented. The TPG jots showed an average read noise of 0.26e- rms with a best-case read noise of 0.19e- rms at 25C, while the average read noise is 0.22e- rms with a best-case of 0.17e- rms at -70C. The noise probability density peak clearly shifted towards the lower read noise regime at lower temperature as shown in Figure 8 (right). The reduction of the read noise at low temperature is mainly due to the reduction of 1/f noise [7]. The noise trend with the temperature will help us understand the nature of our 1/f noise and guide future design for better noise performance. Future testing will include the read noise at intermediate temperatures. The demonstrated low-temperature operation also shows the possibility for QIS to find applications in scientific imaging which benefits from low temperature.

Figure 8. (left) A scatter plot of the voltage-referred read noise versus conversion gain of TPG jots at room temperature and -70C; (right) A histogram of the read noise of the TPG jots with at room temperature and -70C.

# 3.3 Bandpass filtering for noise elimination

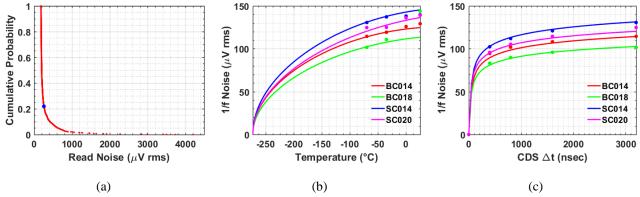

1/f noise reduction from the in-pixel SF was demonstrated by cooling. Further 1/f noise reduction can be achieved via bandpass filtering controlled by CDS time difference [8]. Figure 6 (right) shows the timing diagram applying bandpass

filtering to SF noise testing. At the beginning of the measurement, the FD was reset and the SWs of the pixel were emptied. The SF output was sampled by two CDS capacitors sequentially. Adjusting the  $\Delta t$  between the falling edge of the two CDS sampling signals, the SF noise in different frequency regions can be characterized. The CDS samples were readout by the PGA using a CMS process to suppress the noise contributions from the PGA and the subsequent readout chain electronics. With 38 CMS readout cycles, the noise contribution from the PGA and the subsequent readout chain becomes negligible. Since the chip was placed in a dark chamber during the testing, the photon shot noise is eliminated. Thus the total measured noise should only include the SF noise and the kTC noise from the CDS capacitor. The read noise with different types of SFs is investigated at different CDS  $\Delta t$  and temperatures. Different types of SFs are tested including:

- BC014 BC SF with 0.14μm/0.22μm (W/L) size.

- BC018 BC SF with 0.18μm/0.22μm (W/L) size.

- SC014 BC SF with  $0.14 \mu m/0.22 \mu m$  (W/L) size.

- SC020 BC SF with 0.20μm/0.22μm (W/L) size.

For each type of SF, an array of 256(H)x5(V) jots was tested. An example of the measured read noise distribution from 1280 jots at room temperature is shown in Figure 9(a). Since the amplitude of random telegraph noise (RTN) is relatively big, the RTN jots (about 50 jots) are excluded for 1/f noise analysis. Other noisy jots not showing RTN but are highly-possible RTN jots are also excluded. Only the quietest 1000 jots (highlighted in Figure 9(a)) not showing RTN were analyzed for each type of SF. Meanwhile, the kTC noise from the CDS capacitors, which is approximately equal to the measured noise when CDS  $\Delta t$  is 0, was subtracted as well. Figure 9(b)(c) shows the decreasing trend of 1/f noise with lower temperature and smaller CDS  $\Delta t$ . The trend is fitted using the unified 1/f noise model [7]. The 1/f noise is bigger for a smaller area device, indicating the noise degradation trend with device scaling. And buried-channel SFs have lower 1/f noise than surface-channel SFs, probably due to the less trap density in the bulk compared to the silicon-oxide interface.

Figure 9. (a) An example of the measured read noise distribution from 1280 TPG jots with SC014 SF at RT. The blue point highlights the quietest  $1000^{th}$  jots. (b)(c) Fitted (lines) and measured (circles) 1/f noise for 4 types of SFs. (b) 1/f noise versus temperature with  $1\mu$ A bias current and CDS time difference  $\Delta t = 3.2\mu s$ ; (c) 1/f noise versus CDS time difference  $\Delta t$  with  $1\mu$ A bias current and -70C temperature. Both sets of data are fitted using the unified 1/f noise model in [7].

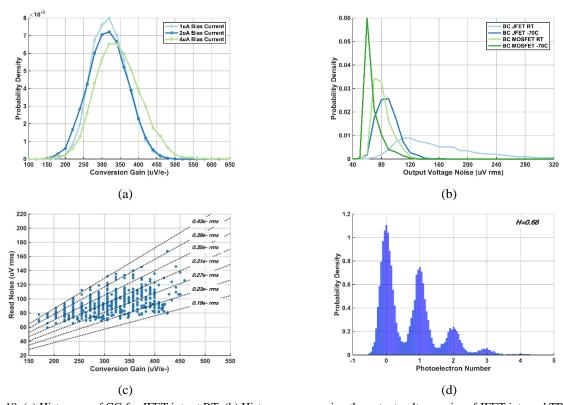

#### 3.4 JFET SF for further noise reduction

While the JFET jots were anticipated to have a lower noise than the TPG jots, room temperature tests show that the JFET jots have fairly high noise, enough that the PCH method could not be used to characterize the devices (i.e. read noise >0.45e- rms). Instead, to characterize the CG of the JFET devices, the photon transfer curve (PTC) method was used, where 1000 frames were used per light level, the PGA gain was set to 2x, and the PTC was evaluated for each JFET jot. The histogram of the CG for the JFET jots biased at  $1\mu$ A,  $2\mu$ A and  $4\mu$ A is shown in Figure 10a, demonstrating some devices with CG as high as  $595\mu$ V/e-. The JFET devices completely remove the parasitic SF gate-oxide capacitance from the FD and replaces it with a PN junction capacitance, which is significantly lower, resulting in a higher CG. The mean CG for  $1\mu$ A,  $2\mu$ A and  $4\mu$ A is  $330\mu$ V/e-,  $326\mu$ V/e- and  $354\mu$ V/e- respectively. While we expect CG to go up with bias current, the data shows that the  $2\mu$ A data includes more lower-CG devices than the  $1\mu$ A data as some devices are out of the input common-mode range at  $1\mu$ A bias current. However, we also note that there is an extremely large variation in the CG of more than 14.4%, which is problematic for the thresholding employed in a QIS for binary imaging. The implant

process for the JFET devices needs to be optimized in the future to possibly improve this large spread and bring up the mean CG.

To characterize the noise of these devices, the JFET jots were placed in the dark, 100k continuous readouts were collected and the standard deviation was calculated as the noise. The results for 1024 JFET devices is shown in Figure 10b, under the BC JFET RT label. For reference, the voltage noise data for the TPG devices is included on the plot under BC MOSFET RT. The higher noise exhibited by the JFET jots is currently not understood, as, in theory, the noise should be significantly lower due to reduced interactions with the Si/SiO<sub>2</sub> interface. The current hypothesis is that there may be some excess noise caused by leakage from the channel to the substrate increasing the current noise due to a weak channel confinement. In testing the JFET devices, we also saw devices demonstrating RTN noise, which should not occur, but may be present if the channel is not sufficiently buried from the interface traps.

Figure 10. (a) Histogram of CG for JFET jots at RT; (b) Histogram comparing the output voltage noise of JFET jots and TPG jots at RT and -70C; (c) Scatter plot showing the CG vs output voltage noise for the JFET jots at -70C; (d) PCH of the golden JFET jot with 0.187e-r.m.s. read noise at -70C.

To further explore the noise performance of the new JFET devices, the devices were cooled to -70C. At this temperature the noise of the JFET devices was sufficiently reduced to allow for characterization via the PCH, possibly due to a reduction in the previous mentioned leakage hypothesis. Figure 10b shows the noise results under BC JFET -70C, which are calculated from the CG and read noise extracted via the PCH from 1024 JFET devices. We see a fairly large reduction in the mean noise while the more limited tail is caused by the PCH is only being valid for read noise >0.45e- rms. The collected TPG data at -70C is included in Figure 10b for comparison under BC MOSFET -70C. A scatter plot of the CG and the output voltage noise is shown in Figure 10c, where we also see no clear trend, but note a very large scatter especially compare to Figure 7(left). Figure 10d shows the PCH for the lowest read noise JFET jot at -70C which had a CG of  $425\mu$ V/e- and a read noise of 0.187e- rms. Furthermore, in doing the PCH testing, we noted a "RTN-like" noise that occurred during the CMS readout, which was present in light, and was not present in dark conditions. The exact cause of this has not been identified, but it seems this effect is increasing the read noise of the JFET jots.

A summary comparing the TPG, PTR and JFET jot devices is shown in Table I, including some other key pixel parameters shared by all the devices.

Table I. Specifications of the 1Mjot single-bit QIS.

| Jot type                       | TPG                                   | PTR          | JFET        |

|--------------------------------|---------------------------------------|--------------|-------------|

| Process                        | 45nm (jot layer), 65nm (ASIC layer)   |              |             |

| Jot pitch                      | 1.1µm                                 |              |             |

| Array                          | 1024 (H) x 1024 (V)                   |              |             |

| Conversion Gain on column @ RT | 345μV/e-                              | 368μV/e-     | 330μV/e-    |

| Conversion Gain Variation @ RT | 2.6%                                  | 2.6%         | 14.4%       |

| Input Referred Noise @ RT      | 0.23e- r.m.s.                         | 0.21e- r.m.s | -           |

| Input Referred Noise @ -70C    | -                                     | -            | 0.3e- r.m.s |

| Quantum Efficiency @ RT        | 71% @ 450nm, 79% @ 550nm, 69% @ 650nm |              |             |

| Dark current @ RT (60C)        | 0.16e-/s/jot (1.06e-/s/jot)           |              |             |

| Field rate                     | 30fps (analog)                        |              |             |

#### 4. ACKNOWLEDGMENTS

The authors appreciate the sponsorship and collaboration of Rambus Inc. in the initial stages of this work, as well as the support and collaboration of the Taiwan Semiconductor Manufacturing Company (TSMC). The characterization work was sponsored by the DARPA DETECT program through Army Research Office (ARO) Cooperative Agreement Number W911NF-16-2-0162. The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the Army Research Office or the U.S. Government. The U.S. Government is authorized to reproduce and distribute reprints for Government purposes notwithstanding any copyright notation herein.

# REFERENCES

- [1] Fossum, E.R., "What to do with sub-diffraction limit (SDL) pixels? a proposal for a gigapixel digital film sensor (DFS)," in IEEE Workshop on CCDs and Adv. Image Sensors, Karuizawa, (Japan, June 2005). http://www.imagesensors.org/Past%20Workshops/2005%20Workshop/2005%20Papers/54%20Fossum.pdf

- [2] Fossum, E. R., Ma, J., Masoodian, S., Anzagira L. and Zizza, R., "The quanta image sensor: every photon counts," MDPI Sensors, 16(8), p. 1260, (2016). https://doi.org/10.3390/s16081260

- [3] Ma, J., Masoodian, S., Starkey, D., and Fossum, E.R., "Photon-number-resolving megapixel image sensor at room temperature without avalanche gain", OSA Optica, vol. 4, no. 12, pp.1474-1481, December 2017. https://doi.org/10.1364/OPTICA.4.001474

- [4] S. Masoodian, J. Ma, D. Starkey, T.J. Wang, Y. Yamashita, and E.R. Fossum, "Room temperature 1040fps, 1 megapixel photon-counting image sensor with 1.1um pixel pitch," in Advanced Photon Counting Techniques XI, Proc. of SPIE, Vol. 10212, April 2017. https://doi.org/10.1117/12.2277794

- [5] J. Ma and E.R. Fossum, "Analytical modeling and TCAD simulation of a quanta image sensor jot device with a JFET source-follower for deep sub-electron read noise," IEEE J. Electron Devices Society, vol. 5, no. 1, pp. 69-78, January 2017. https://doi.org/10.1109/JEDS.2016.2618721

- [6] D. A. Starkey and E. R. Fossum, "Determining conversion gain and read noise using a photon-counting histogram method for deep sub-electron read noise image sensors," IEEE J. Electron Devices Society, vol. 4, no. 3, pp. 129–135, May 2016. https://doi.org/10.1109/JEDS.2016.2536719

- [7] K. K. Hung, P. K. Ko, C. Hu, and Y. C. Cheng, "A unified model for the flicker noise in metal-oxide-semiconductor field-effect transistors," IEEE Trans. Electron Devices, vol. 37, no. 3, pp. 654–665, 1990. https://doi.org/10.1109/16.47770

- [8] C. Y.-P. Chao, H. Tu, T. Wu, K.-Y. Chou, S.-F. Yeh, and F.-L. Hsueh, "CMOS image sensor random telegraph noise time constant extraction from correlated to uncorrelated double sampling," IEEE J. Electron Devices Society, vol. 5, no. 1, pp. 79–89, 2017. https://doi.org/10.1109/JEDS.2016.2623799